|

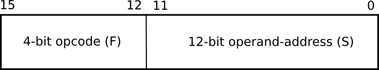

All the instructions in MU0 processor instruction-set are of fixed-length of 16-bit. First 4 MSBs are the op-code bits which uniquely indicate each instruction while remaining 12 LSBs indicate address of the non-implicit operand.

0 Comments

A few posts henceforth are dedicate to an example processor named MU0. The name comes from the Manchester University. MU0 is indeed an abstract design, never actually implemented but designed for study purpose at the university level. The study of MU0 design is really a good entry point for learning the processor designing. Getting into the technical things, MU0 is a 16-bit processor. This means that its ALU is capable on performing operations on 16-bit wide operands. And obviously, the accumulator register is a 16-bit register. Further, the instructions are also 16-bit, with a 12-bit address space. So, (2^12 * 16)-bit i.e. 8 kilobyte or 4 kilo-word [here word is 16-bit] memory can be accessed. The MU0 instructions are fixed-format, fixed-length instruction with 1-operand address. That is, one of the operand and the destination of ALU operations is always implicit, which is accumulator register. The MU0 implements total eight instructions in its instruction set. These instructions can be used to run some not-so-complex but useful programs. All these facts make the design of MU0 processor simple to study. Let's start with the instruction set of MU0 in next post. more on Manchester University computers here. Connect with Digital Byte on facebook to get updates. The processors do not hold a large memory inside them. Whatever storage is available to a processor, is in the form of a few registers. The registers in processor are limited in number and they often are used for some special purpose and some used for general purpose storage.

Let's go through some kinds of registers used inside processors: |

Like facebook page to get updates :

ArchivesCategories

All

|

RSS Feed

RSS Feed